# Electroluminescence (EL) of photovoltaic modules – Terms and classification

VDE SPEC 90031 V1.0 (en)

### **Preface**

Publication date of this VDE SPEC: 06.01.2025.

No draft of this VDE SPEC has been published.

This VDE SPEC is the result of the "PV-Riss" project as part of the "WIPANO – Knowledge and Technology Transfer through Patents and Standards" initiative funded by the Federal Ministry of Economic Affairs and Climate Action (BMWK) (funding reference FKz 03TN0033).

This VDE SPEC is not part of the VDE regulations or the German body of standards. In particular, this VDE SPEC is not a technical rule within the meaning of § 49 EnWG.

The authors of this VDE SPEC are:

- Jäckel Bengt, Fraunhofer-Center für Silizium-Photovoltaik (CSP)

- Paul Schenk, Fraunhofer-Center für Silizium-Photovoltaik (CSP)

- Stephan Rupp, Hanwha Q CELLS GmbH

- Max Köntopp, Hanwha Q CELLS GmbH

- Gottschalg Ralph, Fraunhofer-Center für Silizium-Photovoltaik (CSP) / Hochschule Anhalt (HSA)

- Kirch, Jochen, Ing.-Büro Kirch (Kirch)

- Buerhop-Lutz Claudia, Forschungszentrum Jülich GmbH, IEK-11, HI ERN (HIERN)

- Winkler, Thilo, Forschungszentrum Jülich GmbH, IEK-11, HI ERN (HIERN)

- Linsenmeyer Aswin, Sunset Energietechnik GmbH (Sunset)

- Gerhard Kleiss, 8.2 Arp & Kleiss GmbH (8.2)

- Radacki Dominika, Deutsche Kommission Elektrotechnik Elektronik Informationstechnik in DIN und VDE (DKE)

- Reuter Anna, Deutsche Kommission Elektrotechnik Elektronik Informationstechnik in DIN und VDE (DKE)

We would like to take this opportunity to thank the experts for their valuable contributions and suggestions.

Despite great efforts to ensure the correctness, reliability and precision of technical and non-technical descriptions, the VDE SPEC project group cannot assume any explicit or implicit guarantee for the correctness of the document. The use of this document is made in the knowledge that the VDE SPEC project group cannot be held liable for damages or losses of any kind. The use of this VDE SPEC does not release the user from responsibility for his own actions and is therefore at his own risk.

In the course of manufacturing and/or introducing products into the European Single Market, the manufacturer must carry out a risk analysis in order to determine which risks the product may entail. After carrying out the risk analysis, he evaluates these risks and, if necessary, takes suitable measures to effectively eliminate or minimize the risks (risk assessment). This VDE SPEC does not release the user from this responsibility.

Attention is drawn to the possibility that some elements of this document may infringe patent rights. VDE is not responsible for identifying any or all patent rights in this respect.

# **Executive Summary**

Different pattern can be observed by electroluminescence (EL) imaging of crystalline c-Si cells and modules. Different failure or observation catalogues exist, however, no standardized catalogue existed, yet.

With this VDE-SPEC the project teams try to close this gap and includes a naming convention and a chess-pattern location scheme. Four main categories are defined for EL observations. In those different sub-categories are stated for further classification. For each class example images are given.

# **Contents**

| Intro | ntroduction                                             |    |  |

|-------|---------------------------------------------------------|----|--|

| 1     | Scope                                                   | 1  |  |

| 2     | Normative references                                    | 1  |  |

| 3     | Terms and definitions                                   | 2  |  |

| 4     | Symbols and abbreviations                               | 2  |  |

| 5     | General                                                 | 3  |  |

| 5.1   | Typical c-Si PV module design                           | 3  |  |

| 5.2   | Cell location nomenclature                              | 3  |  |

| 5.3   | Requirements for EL-Images                              | 5  |  |

| 6     | Types of EL-observations                                | 6  |  |

| 6.1   | Single crack                                            | 6  |  |

| 6.1.1 | Complete                                                | 6  |  |

| 6.1.2 | Incomplete                                              | 6  |  |

| 6.2   | Multiple cracks                                         | 7  |  |

| 6.2.1 | Double                                                  | 7  |  |

| 6.2.2 | Multiple crack pattern                                  | 7  |  |

| 6.2.3 | Dendritic shaped crack structures (worst case of 6.2.2) | 8  |  |

| 6.2.4 | Tiny X-V-shape cracks                                   | 8  |  |

| 6.3   | Anomalies in electrical circuit                         | 9  |  |

| 6.3.1 | Finger interruptions                                    | 9  |  |

| 6.3.2 | Missing cell to cross connector joint                   | 9  |  |

| 6.3.3 | (completely) Dark cells and strings                     | 10 |  |

| 6.3.4 | PID, LeTID, UVID                                        | 10 |  |

| 6.3.5 | Severe mechanical loads                                 | 11 |  |

| 6.4   | Miscellaneous                                           | 11 |  |

| 6.4.1 | Dark spots                                              | 11 |  |

| 6.4.2 | Wafer related structure                                 | 12 |  |

| 6.4.3 | Belts structures                                        | 12 |  |

| 6.4.4 | Solar Cell "artefacts"                                  | 13 |  |

| 6.4.5 | Grayish and darker areas                                | 13 |  |

| 6.4.6 | Scratches                                               | 14 |  |

| Bibli | 15                                                      |    |  |

# List of figures

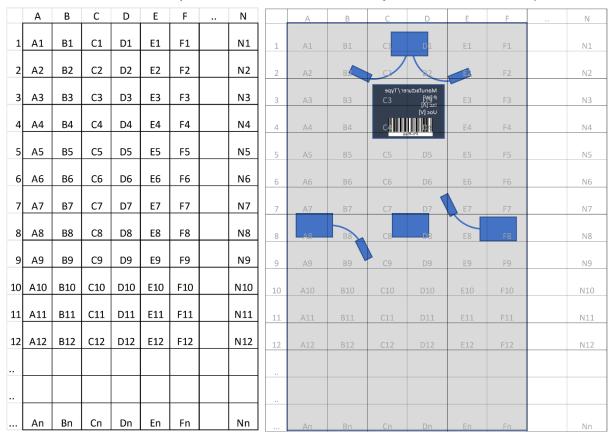

| Figure 1 – Cell location / position nomenclature. View from frontside – left as e.g. visible in EL/visual inspection, right look through to locate junction box(es) and nameplate                    |           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| sticker                                                                                                                                                                                              | 4         |

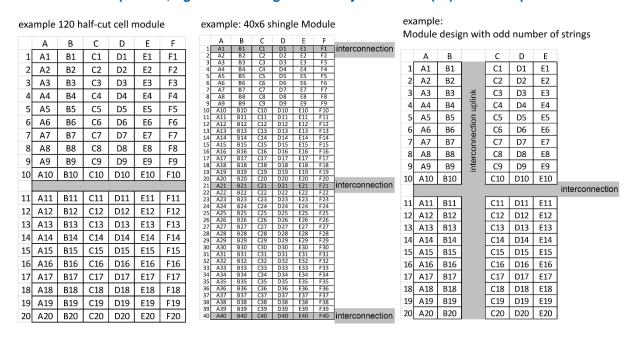

| Figure 2 – Example layouts of different module designs                                                                                                                                               | 4         |

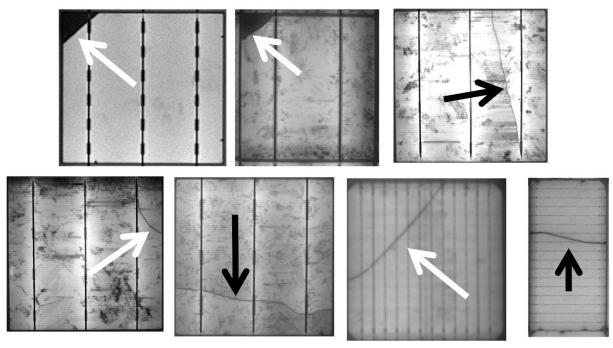

| Figure 3 – Complete single crack                                                                                                                                                                     | 6         |

| Figure 4 – Incomplete single crack                                                                                                                                                                   | 6         |

| Figure 5 – Double crack                                                                                                                                                                              | 7         |

| Figure 6 – Multiple crack pattern                                                                                                                                                                    | 7         |

| Figure 7 – Multi / Dendritic shaped crack structures                                                                                                                                                 | 8         |

| Figure 8 – Tiny X-V-shape cracks                                                                                                                                                                     | 8         |

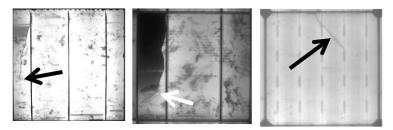

| Figure 9 – Example images of finger interruptions a) typically caused during cell metallization printing b) interruptions at busbar possibly caused by misaligned ribbons on cell durable soldering. |           |

| Figure 10 – Examples of missing (or broken) solder bonds to cross connector                                                                                                                          | 9         |

| Figure 11 – Completely dark cells during defects in electric circuitry. left: shorted individual cells within a string, right: shorted bypass diode that reduced module output to 2/3                | 10        |

| Figure 12 – Example images of a) PID b) LeTID c) UVID                                                                                                                                                | 10        |

| Figure 13 – Example images of a) severe homogeneous applied static load b) Point-like loa caused by impact such as larger hail c) severe impact with glass breakage                                  | ds<br>11  |

| Figure 14 – Dark spots on different cell formats and cell cuts                                                                                                                                       | 11        |

| Figure 15 – a) Rings in the mono crystalline wafer, b) darker regions in multi-crystalline wafer (cells) caused by position of wafer in brigg                                                        | ers<br>12 |

| Figure 16 – Belt-like pattern, typically across the full cell                                                                                                                                        | 12        |

| Figure 17 – Different, often reoccurring, shaped darker/brighter areas within the solar cells                                                                                                        | 13        |

| Figure 18 – Grayish und darker areas of the cell, differently shaped, different in size and brigh-ness                                                                                               | 13        |

| Figure 19 – Different kinds of scratches on c-Si solar cells                                                                                                                                         | 14        |

### Introduction

Alongside wind power, photovoltaics (PV) is the world's most important renewable energy source for the CO2-free generation of electrical energy. The share of photovoltaics in the German electricity mix is increasing every year and with it the requirements for smooth and predictable operation.

The EU targets under the Green Deal envisage a reduction in CO2 emissions of 55% by 2030 and 100% by 2050. A huge effort is required to achieve these ambitious targets. If we now take into account the fact that e-mobility and the conversion of building heating from fossil fuels to electric heat pumps will significantly increase demand, an increase in electrical energy is to be expected.

In addition to a rapid expansion of renewable energy generation, it must be ensured that the service life of existing PV systems is extended as far as possible. This includes ensuring the framework conditions for both old and new systems. However, there is also a risk that many newer systems will have to be taken off the grid due to premature faults, defects in the backsheets or glass breakage of the PV modules.

This VDE SPEC provides guidelines for the assessment of abnormalities observed in c-Si PV module EL images which are taken either end-of-production line, incoming good inspection, at the installation site or later during operation of the PV power plant.

Despite various existing fault catalogues, scientific publications [1]-[7]<sup>1</sup> and classifications, there are no generally recognized, binding evaluation standards or a forecast that describes the effect on the energy yield of a system.

The leading scientific model for evaluation is that of Koentges [5], which calculates the maximum possible crack-related separation and equates the area with the power loss. This allows an estimation of the maximum expected effects, which, however, must be confirmed in individual cases with the help of laboratory power measurements and represents a worst-case estimate.

Studies on the repetition of power measurements show a clear variance in the values for cracked PV modules [8]. However, there is a certain degree of subjectivity in the assessment. There is still a need for clarification in the prognosis, as dynamic mechanical load (ML) and thermomechanical load alone, for example, cause rather low power losses [10][11]. Only the combination of ML with temperature cycles shows the influence of mechanically induced cracks on the long-term behaviour [10]-[14]. The correlation with field data has also only been investigated in individual cases [14]. A detailed description of the anomalies and observations described here can be found in [15].

# 1 Scope

This VDE SPEC contains a classification of abnormalities for electro-luminescence (EL) images of c-Si PV cells and modules. This includes four main categories for grouping where each group has additional sub-groups. Each abnormality is described and, if possible, a high-resolution EL image is given as example.

The VDE SPEC is applicable for crystalline silicon modules currently manufactured and installed in various locations and mounting situations over the last decades, which only need to be classified according to their appearance and the faults that have occurred.

Other inspections and tests necessary for safe operation, such as testing of junction boxes, cables and plugs, must be carried out in accordance with other inspection standards.

Additionally, more stringent assessments may need to be carried out if the PV system is installed on system-critical infrastructure (e.g. hospital) or otherwise endangered buildings / installations (e.g. region with high risk of forest fires, roofs at risk of fire). Fire and other safety-relevant standards must be complied with.

# 2 Normative references

The following documents are referred to in the text in such a way that some or all of their content constitutes requirements of this document. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

<sup>&</sup>lt;sup>1</sup> Numbers in square brackets refer to the Bibliography.

IEC TS 60904-13:2018, Photovoltaic devices - Part 13: Electroluminescence of photovoltaic modules

IEC 60904-3, Photovoltaic devices – Part 3: Measurement principles for terrestrial photovoltaic (PV) solar devices with reference spectral irradiance data

IEC 61730-1:2023, Photovoltaic (PV) module safety qualification – Part 1: Requirements for construction

### 3 Terms and definitions

For the purposes of this document, the following terms and definitions apply.

ISO and IEC maintain terminological databases for use in standardization at the following addresses:

- ISO Online browsing platform: available at https://www.iso.org/obp

- IEC Electropedia: available at https://www.electropedia.org/

### 3.1

# Standard Test Conditions (STC) per IEC 60904-3

Standard Test Conditions: 25°C, 1000W/m², AM 1.5

### 3.2

### manufacturer

any legal entity manufacturing a product or has a product designed or manufactured, and markets that product under its name or trademark

[SOURCE: IEC 61730-1:2023, Term 3.1.5]

### 3.3

# **Electro-Luminescence (EL)**

Emission of optical radiation resulting from the application of electrical energy

### 3.4

### Crack in c-Si cell (EL)

Fracture within the crystalline wafer for the solar cell. Two types of cracks are defined:

- Crack complete: Crack is called complete if it starts AND ends at the edge of the cell

- Crack incomplete: Crack is called incomplete, if it ends randomly on the solar cell

# 3.5

# silicon solar cells wafers

Typically c-Si cells are made from either mono-crystalline or multi-crystalline wafers. Their size can vary from 4" to today's M12.

- Mono-material: Single- or mono-crystalline Silicon wafers exhibit an almost ideal crystallographic lattice structure extending across the entire wafer.

- Multi-material: Multi- or poly-crystalline wafers consist of numerous areas (or grains) adjacent to each other but separated by grain boundaries. While the crystalline structure within one such grain is close to mono-crystalline, the lattice orientation from one grain to another varies.

# 4 Symbols and abbreviations

| Abbreviation | description                                                                                                                                                                                                                                                                               |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AI-BSF       | Aluminium Back Surface Field: reduction of surface recombination velocity (performance improvement) by printing and firing a full Aluminium layer on the rear of the solar cell. This was the first, large-scale approach in the solar cell manufacturing process. Mostly obsolete today. |

| PERC         | Passivated Emitter and Rear Cell: a dielectric layer introduced at the rear side of the cell further reduces surface recombination, while also increasing the rear surface reflection.                                                                                                    |

| TOPCon       | Tunneling Oxide Passivated Contacts: A layer of poly-Silicon/Silicon oxide on the rear cell side giving improved passivation properties.                                                                                                                                                  |

| HJT | Heterojunction Technology: Additional amorphous, doped Silicon layers on the front and rear of a crystalline Silicon cell resulting in good passivation and absorption properties.                                                                                         |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IBC | Interdigitated Back Contact: Positive and negative electrical contacts are both situated at the rear of the cell. No visible structures on the front side of the solar cell (difference to MWT). This means, amongst other advantages, less shading on front side of cell. |

| MWT | Metallisation Wrap Through: Positive and negative electrical contacts are both situated at the rear of the cell. Compared to IBC there is a visible front side metallization. Still, this means, amongst other advantages, less shading of the cell.                       |

| ВВ  | Busbar – these structures are located in varying numbers on the cells and collect the current and cell interconnectors are soldered on them.                                                                                                                               |

| FS  | Frontsheet per IEC 61730-1                                                                                                                                                                                                                                                 |

| BS  | Backsheet per IEC 61730-1                                                                                                                                                                                                                                                  |

# 5 General

# 5.1 Typical c-Si PV module design

Traditionally, solar modules have been assembled in a Glass-Backsheet variant. The solar cells are embedded in between the front glass and a rear backsheet made out of a polymer material (EVA for instance). While this backsheet offers protection against detrimental environmental conditions like moisture, dust and UV radiation, it offers little protection against any mechanical impact.

Glass-Glass modules on the other hand offer additional resilience against environmental and mechanical damage. The cells are encapsulated in between two panes of glass. Depending on the cell design and the installation location of the module, additional performance improvements are possible by light which is absorbed through the backside of the module.

Traditionally, the solar cells that are used in modules were square or square-like. This is true regardless if the wafers were cut from a square brick (multi-crystalline ingot) or a round, mono-crystalline ingot. Cutting these square cells in half or even in thirds offers the advantage of higher voltages and lower currents in a serial connection. Lower currents are advantageous from a power loss perspective.

Contemporary module designs often consist of a combination of serial and parallel connected substrings. A common module configuration for instance consists of 3 submodules connected in series, each with two substrings connected in parallel.

# 5.2 Cell location nomenclature

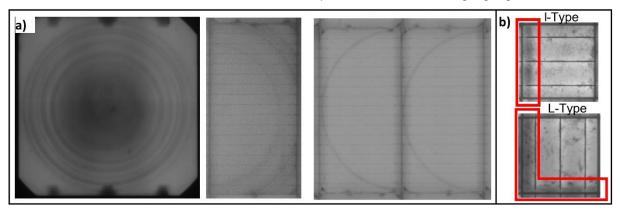

To locate cells in the module the nomenclature in Figure 1 applies. It considers different cell geometries as well as different internal circuitries of the PV module. An example is given in Figure 2.

# Base scheme: cell positions Base scheme: junction box + nameplate

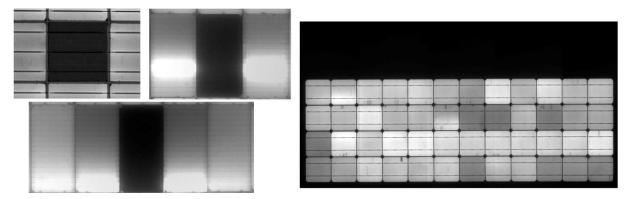

Figure 1 – Cell location / position nomenclature. View from frontside – left as e.g. visible in EL/visual inspection, right look through to locate junction box(es) and nameplate sticker

Figure 2 - Example layouts of different module designs

# 5.3 Requirements for EL-Images

IEC TS 60904-13:2018 defines certain criteria for taking high quality EL-Images. The relevant criteria are taken from there, however only some fundamental recommendations and descriptions can be given here.

Detectors for EL images are typically arrays of light sensing pixels. There are different light-absorbing materials that can be used in the detectors with the most common ones being the Ge, InGaAs, Si or InAs. Each of these semiconducting materials is more or less sensitive to different parts of the spectrum. Consequently, the user should be aware of the detector type and the emitted spectrum of the sample.

The necessary resolution of the sensor is determined by the size of the module and the smallest image feature that is still to be resolved. For instance, if a feature of 2.5 mm is to be resolved on a module dimension of 1600 mm, then 640 pixels are required (the distance between the sample and the detector has to be adjusted for optimal capture of the image).

Sensor resolution = Field Of View (FOV) / smallest detectable feature

The same relation is valid for the other dimension.

When acquiring an image, the angle of view is preferably normal with respect to the sample surface, however it should not be more than 50°. For high-quality images inside, a darkened environment is needed. For measurements outside, perform these at night. IEC TS 60904-13 gives details on how to correct for stray light.

The Sharpness S [mm] is defined as the physical dimension, for which a contrast of 50 % can still be distinguished. IEC TS 60904-13 defines three Sharpness classes with S being

- a) less than or equal to 1.5 mm,

- b) less than or equal to 5.0 mm,

- c) less than or equal to 15.0 mm.

The standard also elaborates on a method to determine this sharpness experimentally. When quantitatively comparing modules, the images should be of similar sharpness classes.

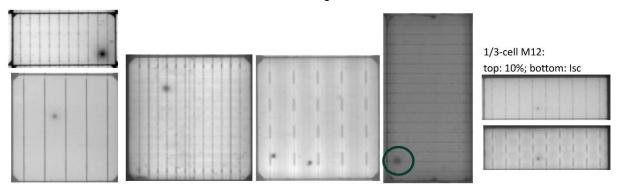

Signal-to-noise ratio (SNR) is also an important factor in the image quality and the ability to distinguish between EL features. The user should be aware that the minimal acceptable SNR levels are different between Laboratory measurements, Industrial/Process Control and Outdoor measurements. Further information is given in IEC TS 60904-13.

EL images can be taken at different current settings where different features will be differently enhanced. Therefor it is important to note the applied current. Typically, a current of  $I_{sc}$  to  $I_{mpp}$  is used for standard imaging. For shunt related features (e. g. PID detection) a current of 10%  $I_{sc}$  is recommended.

# 6 Types of EL-observations

# 6.1 Single crack

# 6.1.1 Complete

**Definition:** A single crack within a single solar cell that is complete.

Possible root cause of defect: cell and module handling, mechanical loads.

Figure 3 – Complete single crack

# 6.1.2 Incomplete

**Definition:** A single crack within a single solar cell that is **incomplete.**

Possible root cause of defect: cell and module handling, mechanical loads.

Figure 4 – Incomplete single crack

# 6.2 Multiple cracks

# **6.2.1** Double

**Definition: Two** cracks within a single solar cell that are **complete or incomplete.**

Possible root cause of defect: cell and module handling, mechanical loads.

Figure 5 - Double crack

# 6.2.2 Multiple crack pattern

**Definition:** More than **TWO** cracks within a single solar cell that are **complete or incomplete.**

Possible root cause of defect: cell and module handling, mechanical loads.

Figure 6 - Multiple crack pattern

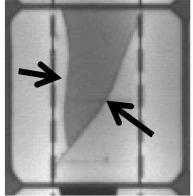

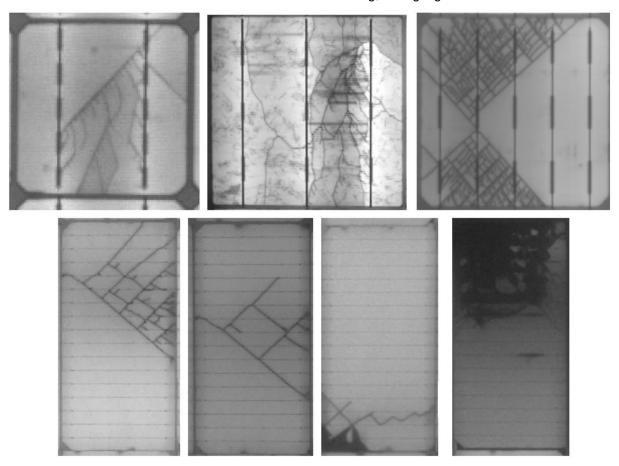

# 6.2.3 Dendritic shaped crack structures (worst case of 6.2.2)

**Definition:** dendritic/branching looking crack pattern across the full cell.

Possible root cause of defect: bad cell and module handling, strong/high mechanical loads.

Figure 7 – Multi / Dendritic shaped crack structures

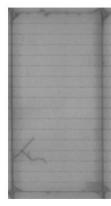

# 6.2.4 Tiny X-V-shape cracks

**Definition:** Short cracks (<30mm total length) within the solar cell, not crossing a BB and not ending at edge of cell, often start at BB or cell cut at position of BB, show 45° angels with respect to BB.

**Possible root cause of defect:** typically cell / string handling during manufacturing, tiny x-shape cracks can be caused by sharp tools from hitting the backsheet.

Figure 8 - Tiny X-V-shape cracks

### 6.3 Anomalies in electrical circuit

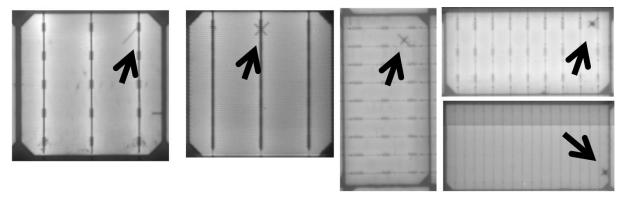

# 6.3.1 Finger interruptions

**Definition:** Solar cell grid finger interruptions, typically a few per cell, repeated in neighbouring cells.

**Possible root cause of defect:** defective mesh during cell printing; miss-aligned ribbons vs BB during soldering.

Figure 9 – Example images of finger interruptions

a) typically caused during cell metallization printing

b) interruptions at busbar possibly caused by misaligned ribbons on cell during soldering.

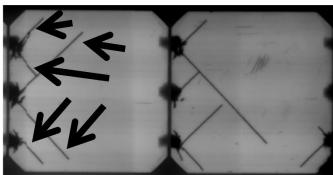

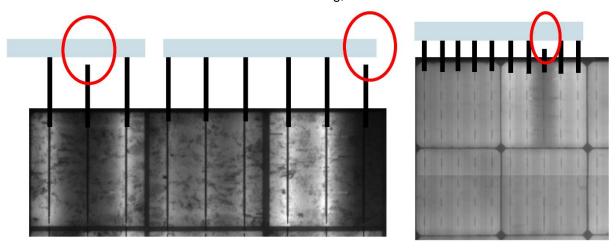

# 6.3.2 Missing cell to cross connector joint

**Definition:** Solar cell interconnection not connected, e.g. by missed soldering or to short cell interconnection ribbon.

Possible root cause of defect: bad or missed soldering, cell connectors too short.

Figure 10 – Examples of missing (or broken) solder bonds to cross connector

# 6.3.3 (completely) Dark cells and strings

**Definition:** totally dark cell or (double)cell-string (no PID).

Possible root cause of defect: shorted cell during stringing, defective bypass diode.

Figure 11 – Completely dark cells during defects in electric circuitry. left: shorted individual cells within a string, right: shorted bypass diode that reduced module output to 2/3

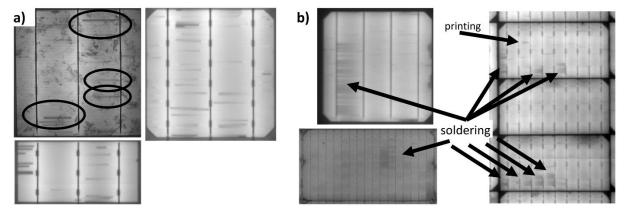

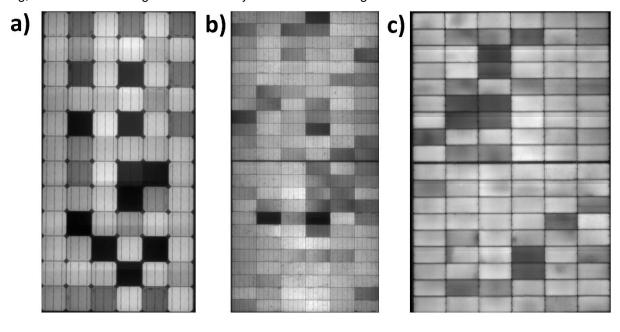

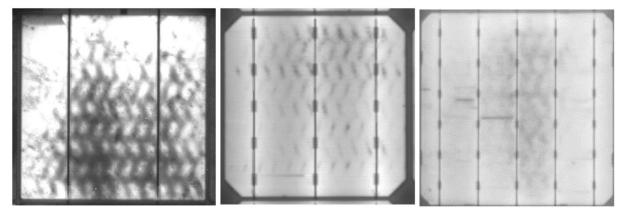

# 6.3.4 PID, LeTID, UVID

**Definition:** totally affected cells with dark or darker grayish appearance.

**Potential root cause of patterned image:** Potential induced degradation (PID), Light and elevated temperature induced degradation (LeTID), UV-induced degradation (UVID), or mixing of cells with different efficiencies. PID, LeTID, UVID pattern are typically visible after outdoor exposure or stress testing, whereas cell mixing is visible directly after manufacturing.

Figure 12 – Example images of

a) PID b) LeTID c) UVID

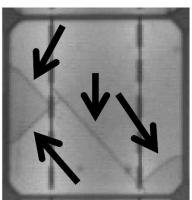

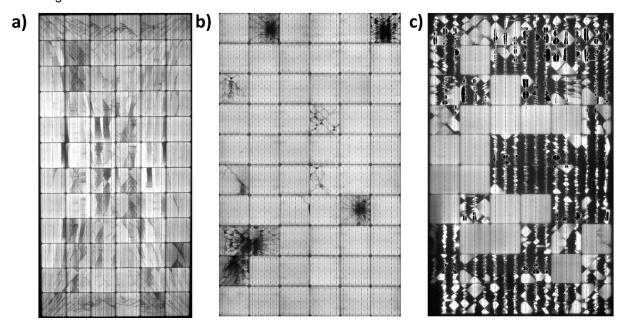

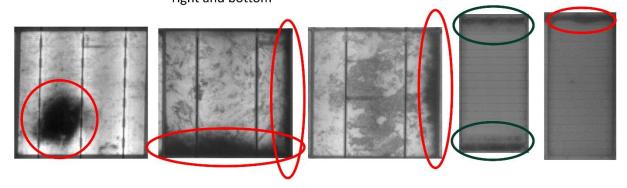

### 6.3.5 Severe mechanical loads

**Definition:** Severely cracked cells with special pattern, originated from different types of strong mechanical impacts.

**Potential root cause of defect:** Severe snow loads (a), hail impact (b) or severe impact, including broken glass.

Figure 13 – Example images of

a) severe homogeneous applied static load

b) Point-like loads caused by impact such as larger hail

c) severe impact with glass breakage

## 6.4 Miscellaneous

# 6.4.1 Dark spots

**Definition:** Tiny dark areas (mm-range), typically circular in shape within the solar cell, no known impact on long term stability.

Possible root cause of defect: contaminations on ingot, wafer or cell level.

Figure 14 - Dark spots on different cell formats and cell cuts

## 6.4.2 Wafer related structure

**Definition:** Circular rings within mono-crystalline cells, can't occur in multi-c-Si material; darker grayish areas along one or two cell edges of multi-crystalline cells, can't occur that way in mono-crystalline cells. No known impact on long term stability of AI-BSF and PERC cells, might be different for nextgen cells.

Possible root cause of defect: contaminations and process variations during ingot growth.

Figure 15 – a) Rings in the mono crystalline wafer, b) darker regions in multi-crystalline wafers (cells) caused by position of wafer in brigg

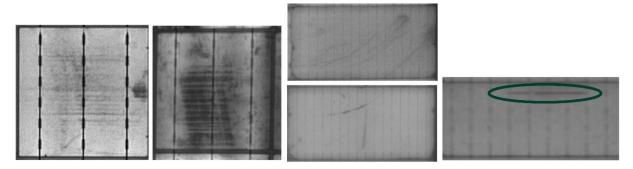

# 6.4.3 Belts structures

$\textbf{Definition:} \ \ \textbf{Belt-like pattern, typically across the full cell, no known impact on long term stability.}$

Possible root cause of features: non-optimal firing process during cell manufacturing.

Figure 16 - Belt-like pattern, typically across the full cell

# 6.4.4 Solar Cell "artefacts"

**Definition:** Different, often reoccurring, shaped darker/brighter areas within the solar cells, no known impact on long term stability.

Possible root cause of features: different stages during cell manufacturing.

Figure 17 - Different, often reoccurring, shaped darker/brighter areas within the solar cells

# 6.4.5 Grayish and darker areas

**Definition:** Grayish und darker areas of the cell, differently shaped, different in size and brightness **Possible root cause of features:** different stages during cell manufacturing such as edge passivation right and bottom

Figure 18 – Grayish und darker areas of the cell, differently shaped, different in size and brighness

# 6.4.6 Scratches

**Definition:** artificial looking pattern with different shapes, but randomly orientated over the cell, differently shaped, different in size and brightness, typically stable structures/pattern.

Possible root cause of features: different stages during cell and module manufacturing by handling tools.

Figure 19 – Different kinds of scratches on c-Si solar cells

# **Bibliography**

- [1] Koentges, M. Bothe, K., "Elektrolumineszenzmessung an PV-Modulen", *Photovoltaik aktuell* **7/8**, 36-40 (2008)

- [2] Jaeckel, B. Arp, J., "Blick in die Zukunft", PV Magazin 1, 8 (2013)

- [3] MBJ PV-Modul Bewertungskriterien, "MBJ PV-Modul Bewertungskriterien Bewertungskriterien für die die PV-Modulprüfung im Mobilen PV-Testcenter", *MBJ*, (2014)

- [4] Koentges, M., Kurtz, S., Packard, C., Jahn, U., Berger, K., Kato, K., Van Iseghem, M. (2013). Review on Failures of Photovoltaic Modules. IEA-PVPS T13.

- [5] M. Köntges, U. Jahn, et.al. "Assessment of PV Modules Failures in the Field", Report IEA-PVPS T13-09:2017, http://www.iea-pvps.org/index.php?id=435

- [6] U. Jahn et al. "Assessment of PV Module Failures in the Field", IEA PVPS Task 13 report (http://www.iea-pvps.org/index.php?id=435)

- [7] U. Jahn et al., "Review on Infrared (IR) and Electroluminescence (EL) Imaging for Photovoltaic Field Applications", Report IEA-PVPS T13-10:2018.

- [8] Buerhop-Lutz, C., T. Winkler, J. Hauch, C. Camus and C. J. Brabec (2019). Qualitätsmanagement rissbehafteter PV-Module. PV-Symposium, Kloster Banz, Bad Staffelstein.

- [9] Buerhop, C., et al., Evolution of cell cracks in PV-modules under field and laboratory conditions. Progress in Photovoltaics, 2018. 26(4): p. 261-272.

- [10] Buerhop-Lutz, C., et al. Influence of the module temperature on the performance and EL-image of precracked PV-modules. in 35th EU-PVSEC. 2018. Brussels, Belgium.

- [11] Pander, M., et al, "Sequential Module Testing: Results and Necessity Discussion", PVSec 2020, online

- [12] Jason Lincoln et al. (2019) "Microcrack Formation in Silicon Solar Cells during Cold Temperatures" University of Central Florida, Orlando, FL, USA, In: Conference Record of the 46<sup>th</sup> IEEE Photovoltaic Specialists Conference

- [13] Buerhop-Lutz, C., et al. Performance Analysis of Pre-Cracked PV-Modules at Cyclic Loading Conditions. in 35th EU-PVSEC. 2018. Brussels, Belgium.

- [14] Buerhop-Lutz, C., T. Pickel, J. Teubner, J. Hauch and C. J. Brabec (2019). Analysis of digitized PV-module/system data for failure diagnosis. 36th EU-PVSEC, Marseille, France.

- [15] Jaeckel, B., et al, "Nomenclature and description of EL observations: Cell cracks and other findings", PVSec 2024, Vienna

- [16] IEC 62446-1:2016+AMD1:2018 CSV (Consolidated Version), *Photovoltaic (PV) systems Requirements for testing, documentation and maintenance Part 1: Grid connected systems Documentation, commissioning tests and inspection*

- [17] IEC 61215-1:2021, Terrestrial photovoltaic (PV) modules Design qualification and type approval Part 1: Test requirements

- [18] IEC 61215-2:2021, Terrestrial photovoltaic (PV) modules Design qualification and type approval Part 2: Test procedures

- [19] IEC 61730-2:2023, Photovoltaic (PV) module safety qualification Part 2: Requirements for testing

- [20] IEC 62446-2:2020, Photovoltaic (PV) systems Requirements for testing, documentation and maintenance Part 2: Grid connected systems Maintenance of PV systems

- [21] IEC TS 62446-3:2017, Photovoltaic (PV) systems Requirements for testing, documentation and maintenance Part 3: Photovoltaic modules and plants Outdoor infrared thermography

- [22] DIN EN ISO 9001:2015, Qualitätsmanagementsysteme Anforderungen (ISO 9001:2015); Deutsche Fassung und englische Fassung EN ISO 9001:2015

- DIN VDE 0105-100/A1 (VDE 0105-100/A1):2017-06, Betrieb von elektrischen Anlagen Teil 100: All-gemeine Festlegungen; Änderung A1: Wiederkehrende Prüfungen

VDE Verband der Elektrotechnik Elektronik Informationstechnik e.V. Merianstraße 28 63069 Offenbach am Main Germany Phone +49 69 6308-0 service@vde.com

www.vde.com